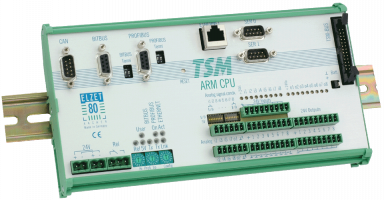

TSM - ARM-CPU

Mit Ethernet rücken die traditionelle IT und die Steuerungstechnik nahe zusammen: Einerseits öffnet der eingebaute Webserver die Steuerung zur Bürowelt hin, andererseits können E/A-nahe Prozeduren direkt auf der TSM-ARM aufgerufen werden.

Die Baugruppe wurde entwickelt, um der steigenden Nachfrage nach direkter Integration in das Ethernet nachzukommen, den Prozessor S3C4530 haben wir gewählt, weil er neben ARM-Kern und Ethernet-Schnittstelle auch noch einen HDLC-Controller integriert hat, der für den BITBUS-Feldbus benötigt wird. Dadurch lassen sich günstig Subnetze aufbauen: Ethernet zur Kommunikation mit der Produktionsplanungsebene und BITBUS für den ggf. auch weiträumig verteilten Feldbereich, der sich durch die Ausdehnungbeschränkunen von Ethernet nicht kostengünstig erreichen lässt.

- 32-Bit-Prozessor S3C4530 mit ARM7TDMI Kern, Cache, DMA, HDLC (Bitbus), 2 32-Bit Timern, 2 ser. Schnittstellen mit Rx und Tx FIFOs, I²C und Ethernet-Controller 10/100MBit

- 4 Megabyte Flash-Eprom, 2 Megabyte RAM mit 32-Bit-Datenbus

- 512K Boot-Flash (sektoriert) erlaubt Betriebssystem-Updates

- mCAT2 Echtzeitkern mit “Express-I/O” für bequemen E/A-Zugriff

- RAM batteriegestützt

- Echtzeituhr mit Kalender

- Zwei RS232 Schnittstellen

- 1 isolierte RS485 Netzwerkschnittstelle (BITBUS)

- Relais (Wechsler) 1A/30V

- Konfigurationssschalter 0..F

- Optional: CAN-Schnittstelle

Prozess-E/A-Bereich:

- Acht Eingänge 24V, optoentkoppelt; wahlweise als Zähler

- Acht PMW Ausgänge 24V, 1,5A, optoentkoppelt und überlastgeschützt

- Acht analoge Eingänge 10 Bit; 0..5V, 0..20mA oder KTY

- Zwei analoge Ausgänge 8 Bit; 0..5V

- Preise

- Webserver

- Hardware

- Prozess-E/A

- Programmierung

- Installation

Preise

auf Anfrage

TSM-ARMCPUEA

Baugruppe mit 32-Bit-Speicher: 4MB Flash-Eprom und 2MB RAM, mit Ethernet und BITBUS, mit E/A (8E/8A, 8E/2A analog)

Batterie und Steckklemmen bitte separat bestellen:

TSM-ARMCPU<XBAT

auf Anfrage

Lithium-Zelle (Li-SOCl2) 3,6V 2,25Ah zur Klettbandbefestigung auf dem Gehäusedeckel

TSM-ARMCPU<XSK

auf Anfrage

Steckersatz für o.a. CPUs: Federkraft-Steckklemmen Raster 3,81mm für die E/As, Steckschraubklemmen 5,08mm für 24V-Versorgung und Relais.

* alle Preise (innerhalb Deutschlands zzgl. MwSt.) ab Werk

Webserver

Für das Ethernet bietet mCAT2 auf der TSM-ARM-CPU einen TCP/IP Stack, der unter Berücksichtigung der Belange eines Echtzeit- Betriebssystems neu geschrieben wurde. Bis zu 3 parallele HTTP-Server sind möglich: Einer wird den allgemeinen Port 80 bedienen (z.B. für eine Webseite mit dem Datenblatt der Baugruppe und Konfigurationseinstellungen), die Anderen können zum Beispiel für mCAT-Servicezwecke benutzt werden.

Für die Darstellung von Webseiten können statische Inhalte (PDF-Datenblätter, GIF-Bilder usw.) komprimiert im Flash abgelegt werden. Ein Hilfsprogramm komprimiert ein vorbereitetes Unterverzeichnis auf Ihrem Windows®-Rechner zu einer herunterladbaren Datei für das Flash-Eprom und setzt den MIME-Typ.

Die Kompression ist so optimiert, dass die De-Kompression wenig Rechenaufwand erfordert, also wenig Last auf der TSM-ARMCPU darstellt.

Eine mCAT Task kann sich beim HTTP-Server als CGI-Funktion anmelden und erhält dann die entsprechenden HTTP-Anfragen. Es steht eine Funktion zum Aufspalten der im HTTP-GET gesandten Daten zur Verfügung und eine dem vprintf() ähnliche Funktion zum Erzeugen der Antwort-HTML-Seite.

Hardware

Das 2 MByte große RAM kann optional über eine große Lithiumzelle gestützt werden, die auf das Gehäuse geklettet wird, sie versorgt auch die I²C-Echtzeituhr hoher Ganggenauigkeit.

Die Batterie eignet sich zur Überbrückung langer Ausfallzeiten und kann im Betrieb ausgewechselt werden. Ebenfalls am I²C-Bus findet sich ein serielles EEPROM mit 64 Worten zur Ablage von Konfigurationsdaten wie Netzwerkadresse, Vorgabegeschwindigkeit der seriellen Schnittstellen etc. Daneben existiert noch ein mit "Config" beschrifteter Drehcodierschalter mit 16 Stellungen, der z.B. vom Endanwender zur Auswahl eines bestimmten Einsatztyps oder Bearbeitungsprogramms verwendet werden kann.

Die isolierte Ethernet-Schnittstelle ist an einer RJ45-Buchse verfügbar und erkennt automatisch 10 bzw. 100 MBit. Die Adresse des Domain-Name-Servers, MAC- und IP-Adresse usw. werden im EEPROM abgelegt.

Die TSM-ARMCPU verfügt über zwei UART Schnittstellen mit FIFOs, die RS232-getrieben auf zwei DB9-Stecker geführt sind. RTS und CTS werden als Quittungssignale unterstützt, DTR wird bei Einschalten der CPU fest aktiviert.

Die eingebaute HDLC-Schnittstelle ermöglicht den Einsatz der TSM-ARMCPU als BITBUS Slave oder Master. Die Schnittstelle ist entsprechend als isolierte RS485-Halbduplex-Schnittstelle ausgeführt. Eine Terminierung, wie sie am physikalischen Ende des Kabels benötigt wird, ist ebenfalls über DIP-Schalter zuschaltbar.

Softwaremäßig bietet die BITBUS-Unterstützung in mCAT direkten Durchgriff vom Master (z.B. PC) bis in das letzte TSM-Modul. Ein Großteil der Express-I/O-Funktionen ist direkt über den BITBUS nutzbar, bei Verwendung des ELZET80 OPC-Servers für BITBUS auch von allen im Netzwerk des Masters befindlichen PCs Aber auch für das gerade vom BITBUS favorisierte Konzept des "Distributed control" ist die TSM-ARMCPU ideal geeignet: Jede mCAT Task kann auch eine BITBUS-Task sein - einschließlich dynamischem Hinunterladen, Aktivierung und Löschen.

Schließlich kann die TSM-ARMCPU auch Gateway zwischen Ethernet und BITBUS sein.

Wenn BITBUS nicht genutzt werden soll, kann eine der beiden RS232-Schnittstellen alternativ über die Halbduplex-Treiber des BITBUS als asynchrone, isolierte RS485-Schnittstelle arbeiten.

Z.B. als "Regler bereit"-Signal bietet ein Relais einen potentialfreien Wechslerausgang mit max. 1A bei 30V. Kombiniert mit der Watchdogschaltung, die bei Spannungseinbrüchen oder Nichtaktivierung durch Software (muss initialisiert werden) RESET auslöst, kann auch eine effektive NOT-Aus-Steuerung realisiert werden.

Prozess-E/A

Für die eigentliche Steuerungsaufgabe stellt die ARMCPUEA-Version der Baugruppe je acht optoentkoppelte Ein- und Ausgänge 24V bereit, dazu acht Analogeingänge und zwei Analogausgänge.

Die acht Eingänge sind auf je 3-polige Stecker für Schraubklemmen gelegt, um einen einfachen Anschluss von Versorgung, Signal und Masse z.B. für übliche (PNP-) Näherungsinitiatoren zu ermöglichen. Die Eingänge haben eine ESD-, Burst-und Surge-feste Schutzbeschaltung mit Tiefpaß und Optokoppler und zeigen über rote Leuchtdioden den Eingangszustand an. Schwellwerte und Ströme entsprechen den Normen. Die Eingänge können als Zähler genutzt werden: Alle acht als Frequenzzähler oder vier als Frequenzzähler und einer als Ereigniszähler oder zwei als Ereigniszähler.

Die acht Ausgänge sind optoentkoppelt und P-schaltend (High-side), d.h. sie versorgen eine geerdete Last, wodurch Sicherheit gegen Erdschlüsse im Kabel gewährleistet ist. Die Ausgänge treiben je 0,7A über den vollen Temperaturbereich bis 70̊C, wobei wegen der Steckverbinder gesamt nicht über 8A entnommen werden dürfen.

An die analogen Eingänge können nicht nur Spannungen zwischen 0 und 5V angelegt werden, über je zwei DIP-Schalter für jeden Eingang sind alternativ auch 0..20mA Prozeßstrom aufzulegen oder direkt Si-Temperatursensoren (2kOhm) wie KTY10 oder KTY82. Für die Analogeingänge ist ein separater Netzteilzweig mit Referenzund Sensorspannungserzeugung aus einer linear geregelten 12V-Zwischenspannung vorhanden. Auf alle durch Express-I/O unterstützte E/A sowie auf die systemglobalen Variablen (Softbus) kann über nodeAccess direkt von einem Windows-Client zugegriffen werden.

Optional ist die TSM-ARMCPU mit CAN-Anschluss über einen DB9-Stecker erhältlich. Für Informationen zur Softwareunterstützung erbitten wir Ihre Anfrage.

Ebenfall optional ist die PROFIBUS-Anschaltung (als Slave) erhältlich. Zwei Drehschalter dienen der Eingabe der Slave- Adresse. Profibus wird von mCAT unterstützt.

An den TSM-Bus-Anschluss können bis zu 16 E/A-Module mit einer Gesamt-Stromaufnahme von 3,5A angeschlossen werden.

Programmierung

Programmierbar ist die ARM-CPU in C auf Basis des portierten mCAT2-Echtzeitkerns, der schon von unseren TLCS900-Produkten bekannt ist. mCAT stellt Zeit und Ereignis gesteuerte Kommunikation durch Nachrichten zwischen Tasks bzw. zwischen Interrupttreibern und Tasks bereit. Die Hardware- Abstraktionsschicht "Express-I/O" erlaubt den Zugriff auf E/A durch Zuweisung von Namen auf beliebige analoge oder digitale Ein- oder Ausgänge. Mit z.B. IN(&kesseltemp) oder OUT(&motor) lassen sich logische Einheiten handhaben, die ggf. auch anderen physikalischen E/As zugewiesen werden können.

Die seriellen Schnittstellen werden durch komfortable Interrupttreiber unterstützt, die mit Start- und Endsequenzprüfung und mit diversen Filterfunktionen parametriert werden können. Datenspeicherung im ausfallsicheren RAM erfolgt unter Zuhilfenahme des BgMEM-Speichers für FIFO-, LIFO- oder Ringspeicherstrukturen.

Für die TSM-ARMCPU gibt es einen sehr empfehlenswerten C-Compiler von Metaware, der aber einen professionellen Preis hat. Für den Versuch empfehlen wir einen gnu-C aus der Linux-Welt, der mit der "Cygwin" Linux-Emulations-DLL auch unter Windows-Betriebssystemen arbeitet. Auf der mCAT Entwicklerdiskette haben wir ein solches Paket für Sie kostenlos geschnürt.

Konvertierungsarbeiten beim Übergang von der TSM-CPUxxH2 beschränken sich auf eventuelle Anpassungen bei den E/A-Zugriffen an Express-I/O vorbei, also z.B. auf Prozessor integrierte Peripherie und auf die Ausrichtung der Variablen auf 4-Byte- Grenzen, die der ARM-Prozessor benötigt.

Das Betriebssystem mCAT wird - wie später die Anwenderprogramme - über einen "Bootmon" (im 8-Bit-Flash) in das Programm-Flash (1Mx32) auf der ARMCPU hinuntergeladen - so profitieren mCAT und Anwenderprogramm vom schnellen 32-Bit- Zugriff.

Alle Programmierung und auch das Löschen von Seiten (Blöcken) im Flash-EPROM erfolgt durch Monitorbefehle oder über den BITBUS. mCAT unterstützt die wahlweise Programmierung ins RAM hinein für den Testbetrieb (durchaus auch autostartend, wenn batteriegestützt) und ins Flash-EPROM.